本周,英特尔为精选的媒体和合作伙伴举办了一年一度的架构日活动。 与之前的迭代一样,该公司透露了有关其计划在未来 12 个月内推向市场的下一代底盘的详细信息。 英特尔已承诺在今年年底前发布其下一代移动和消费类处理器 Alder Lake,今天该公司将分享有关芯片整体设计的大量细节以及一些不错的细节。 . 有关构成这种混合设计的微观结构的详细信息:Golden Cove 和 Gracemont。 这是我们对英特尔披露的分析。

奥尔德湖:英特尔 12国民服役 科尔将军

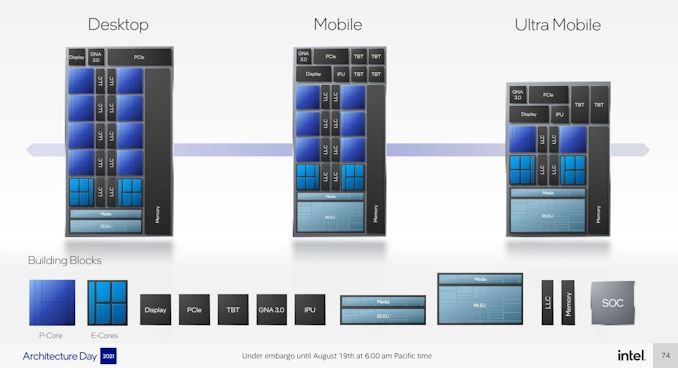

正如之前的公告中提到的,英特尔将以英特尔 12 的名义在台式机和移动平台上推出其 Alder Lake 系列处理器。国民服役 今年晚些时候将推出采用混合技术的 Gen Core 处理器。 这是英特尔基于英特尔7处理节点技术的第二代混合架构,混合设计如下 英特尔 Lakefield 设计 适用于去年推出的小型笔记本电脑。 英特尔术语中混合设计的本质包括一系列高性能内核与多个高效内核的配对。 英特尔已将其简化为 P 核和 E 核这两个术语。

对于 Alder Lake,处理器设计具有基于新 Golden Cove 微架构的性能内核和基于新 Gracemont 架构的效率内核。 我们将在本文中介绍这两种情况,但其想法是 P-core 优先用于需要低延迟的单线程任务,而 E-core 在功率受限或多线程场景中更好。 几乎每个 Alder Lake SoC 都将同时具备,但英特尔尚未披露最终用户产品配置。

每个 P 核都具有提供多线程的能力,而电子核每个核一个线程。 这意味着将有基于 Alder Lake 的三种物理设计:

- 8 个 P 核 + 8 个 E 核 (8C8c / 24T) 台式机,位于新的 LGA1700 插槽上

- 6 P-core + 8 E-core (6C8c/20T) 用于 UP3 移动设计

- 2 P-core + 8 E-core (2C8c/12T) 用于 UP4 移动设计

英特尔通常强调 UP4 移动设计的功率非常低,最高可达 9W,而 UP3 可以覆盖 12W 到 35W(或可能更高)的任何设备,但当被问及这些处理器的功率预算时,它提到英特尔提供了更多细节将在产品发布时跟进。 英特尔已确认客户的最高功率(可能在台式机处理器上)为 125W。

我们在讨论中强调的是模块化英特尔如何配置 Alder Lake。 在众多核心部件选项中,该公司混合并匹配了它认为适合每个市场的最佳部件组合。

这里显示四个电子核心与 P 核心占据相同的物理空间,但台式机将有 32 个 EU(执行单元)用于 Xe-LP 图形(与上一代相同),而两个移动处理器将提供 96 个物理可以根据产品包中的特定行项目禁用它的 EU。

这三款处理器都将配备用于低功耗 AI 任务的下一代英特尔高斯神经加速器 (GNA 3.0)、显示引擎和一定程度的 PCIe,但台式机处理器将拥有更多。 移动处理器只有图像处理单元 (IPU) 和 Thunderbolt 4 (TBT),大型 UP3 移动处理器有四个 Thunderbolt 端口,而较小的 UP4 处理器只有两个。 桌面处理器将没有任何本机 Thunderbolt 连接。

有关桌面处理器 IO 和互连的更多信息

我们将在本文后面介绍有关内核设计的更多详细信息,但英特尔已经展示了有关台式机处理器的一些信息。 我明确断言总共有 16 个内核和 24 个线程,最多 30MB 的非穷尽的 L3/L3 缓存。

与之前迭代的英特尔处理器不同,台式机处理器将支持所有现代标准:DDR5 4800 MB/s、DDR4-3200、LPDDR5-5200、LPDDR4X-4266。 此外,该处理器将启用动态电压频率缩放(也称为 Turbo)并提供改进的超频支持。 最后一项究竟意味着什么,我们目前还不清楚。

英特尔确认有意愿 不是 具有不同内存支持的独立内核设计——所有台式机处理器都将有一个内存控制器,可以实现所有四种标准。 这意味着如果供应商想要使用 LP 内存(通常采用紧凑的外形设计),我们可能会看到内置 LPDDR5 或 LPDDR4X 的主板而不是内存插槽,但我不会把它放在像华擎这样的人面前内置LPDDR5的迷你ITX板。 虽然我们可以期待几乎相同的支持,但尚未透露移动处理器将支持哪些内存架构。

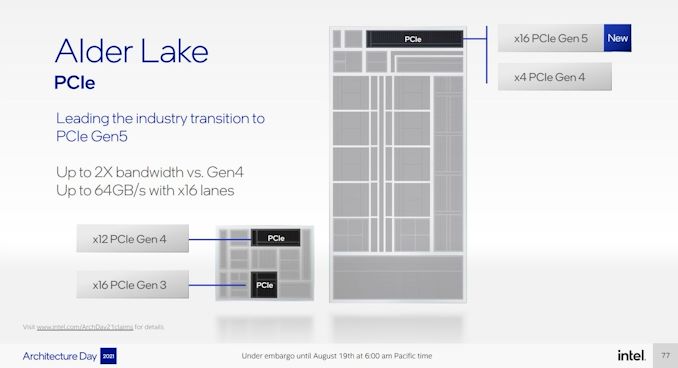

在 PCIe 方面,Alder Lake 桌面处理器将支持 20 个 PCIe 通道,这分为 PCIe 4.0 和 PCIe 5.0。

台式机处理器将有 16 条 PCIe 5.0 通道,我们预计将其分为用于图形的 x16 或用于图形的 x8 和用于存储的 x4/x4。 这将实现 64GB/s 的全带宽。 此外,还有其他四个 PCIe 4.0 通道可提供更多存储空间。 随着 PCIe 5.0 NVMe 驱动器上市,用户可能不得不决定是否要将所有 PCIe 5.0 连接到独立显卡。

英特尔还让我们知道,最高的台式机 Alder Lake 芯片组现在支持 12 通道的 PCIe 4.0 和 16 通道的 PCIe 3.0。 这将允许额外的 PCIe 4.0 硬件使用该芯片组,从而减少 10 千兆位以太网控制器或其他更刺激的项目所需的通道数量。 如果您认为您的 RGB 控制器可以使用更多带宽,英特尔很乐意提供。

Intel 没有透露 CPU 和芯片组之间的带宽连接,尽管我们认为这至少相当于 PCIe 4.0 x4,如果不是更高的话。

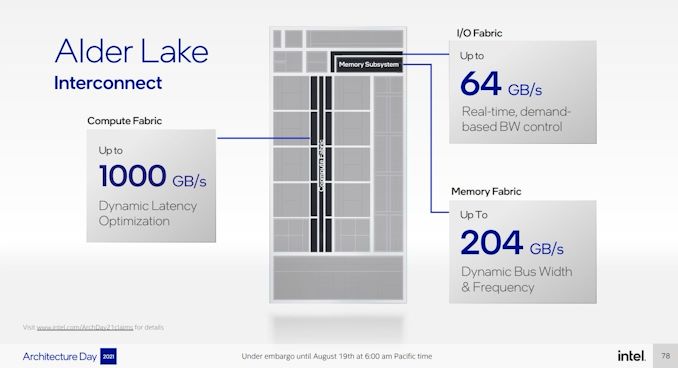

Alder Lake 处理器保留了我们在 Tiger Lake 中实现的双带宽循环,允许 1,000GB/s 的带宽。 我们在问答中从英特尔的问题中了解到,无论使用 P 核还是 E 核,该循环都是完全启用的——当需要较低带宽时,英特尔可以禁用这两个循环之一,无论如何这将节省电量。 在之前的测试中,与低能量过程中的电子核心相比,这个单回路最终可能会产生显着的能量消耗。 (移动处理器也可能如此,这可能会影响移动电池寿命。)

64GB/s 的 I/O 结构符合我们上面看到的 PCIe 5.0 x16 数字,但是,204GB/s 的内存结构带宽是一个令人眼花缭乱的数字。 Alder Lake 具有 128 位内存总线,允许 4 个 32 位 DDR5 通道(DDR5 每个模块有两个 32 位通道,因此还剩下两个模块),但为了在此配置中达到 204 GB/s需要 DDR5 -12750; 英特尔对处理器的评价仅为 DDR5-4800,还不到其一半,因此尚不清楚 204GB/s 的数字来自何处。 从角度来看,英特尔的 Ice Lake 运行速度为 204.8GB/s,这是一个具有 8 个 DDR4-3200 通道的高性能服务器平台。

最后一个芯片提到了 TB4 和 Wi-Fi 6E,但与以前的台式机处理器一样,它源自连接到芯片组的控制器,而不是芯片本身。 移动处理器将内置 TBT,但桌面处理器没有。

这个芯片也指的是 Intel Thread Director,在我们进入微架构分析之前,我们想在下一页讨论它。

"Extreme problem solver. Travel ninja. Quintessential web addict. Browser. Writer. Reader. Incurable organizer."

More Stories

Android 15/One UI 7 正在针对 Galaxy A53、A54 等进行测试

《Helldivers 2》的重大更新招致了负面评价,而且玩家数量并未增加一倍

据报道,谷歌 Pixel 9 将获得一些新的 Gemini AI 功能